# Bias Stress Effects in Low Temperature Amorphous Hf-In-ZnO TFTs Using RF-sputtering HfO2 as High-k Gate Dielectric.

C.A. Pons-Flores<sup>1</sup>, I. Hernández<sup>1</sup>, I. Garduno<sup>1</sup>, I. Mejía<sup>2</sup>, M. Estrada<sup>1</sup>

<sup>1</sup>Sección de Electrónica del Estado Sólido, Depto. Ingeniería Eléctrica CINVESTAV-IPN México 07360, México <sup>2</sup>Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, TX 75080, USA.

Abstract — In this work we analyze the electrical performance, contact resistance and the effects of positive and negative gatebias stress of Hf-In-ZnO/HfO2 thin film transistors. Devices were fabricated using RF-magnetron sputtering at room temperature and fully patterned, with operation voltage below 6 V. Devices with drain-currents up to 2x10-6 A and threshold voltages of ~2 V were analyzed under negative and positive gate bias stress. Devices under negative gate-bias stress showed a slightly threshold voltage shift due to the transistor channel is depleted of electrons at the channel/dielectric interface. Devices under positive gate-bias stress, showed threshold voltage shifts in the negative direction due to the reversible charge/discharge effect of the electrons in pre-existing high-k HfO2 bulk traps. Positive gate-bias stress does not cause any degeneration, since stressed devices tend to recover after 5 mins.

**Keyowrds** — AOSTFTs, stability, contact resistance, hump, bias stressing.

## I. Introduction

In recent years, amorphous oxide semiconductor thin film transistors (AOSTFTs) have attracted the interest of researchers due to their applications in flexible substrates, high mobility, and low-cost and low temperature fabrication process<sup>[1]</sup>. Within AOSTFTs, ZnO-based TFTs have had more enhancements in performance adding materials such as Hf, In, and Ga like Indium-Gallium-Zinc-Oxide (a-IGZO), Indium-Zinc-Oxide (IZO) and Hafnium-Indium-Zinc-Oxide (HIZO). HIZO TFTs have shown a better stability due to a better threshold voltage (V<sub>T</sub>) stability, lowering the conductivity of the active layer, and thus lowering the carrier concentration from 1019 to 1016[2]. Looking for alternative dielectrics to SiO<sub>2</sub> and SiN<sub>3</sub>, high-k dielectrics, such as AlO<sub>3</sub>, HfO, and TiO, have been used in AOSTFTs with deposition techniques such as atomic layer deposition (ALD)<sup>[3]</sup>, pulsed layer deposition (PLD)<sup>[4]</sup> and RF magnetron sputtering<sup>[5]</sup>.

Nevertheless, AOSTFTs still present several instabilities caused by illumination<sup>[6]</sup>, positive and negative bias stress<sup>[7]</sup>, ambient/surface interaction<sup>[8,9]</sup>, simultaneous light exposure/bias stressing [10], surface non-passivated<sup>[11]</sup> and interfacial defects<sup>[12]</sup>. Device performance and stability will depend on the device structure, on the material and thickness of the dielectric and semiconductor, as well as on the fabrication process. The device performance can also be affected by other factors, such as metal contact and contact resistance should be also considered. As it is known, oxide semiconductors are prone to instabilities during the process due to deposition and patterning processes during the formation of source-drain

(S/D) electrodes, therefore, it is critical to analyze the contact resistance, as this analysis is key for the implementation of the TFTs in circuit design.

Researchers have reported  $^{[7,10,13,14]}$  that negative gate bias stress (NGBS) results in negligible changes in  $V_{_{T^{\prime}}}$  subthreshold swing (S) and mobility  $(\mu_{_{FET}})$  when the devices, with dielectrics such as thermal  $SiO_{_{2}}$  and ALD  $AlO_{_{3}}$ , are stressed in the dark, at room temperature and without surface passivation. Nevertheless, during the fabrication process, final annealing and deposition processes at temperatures > 200°C are performed. Some others, have reported a negative  $V_{_{T}}$  shift and S degradation in ZTO  $^{[6]}$ , IZO  $^{[15]}$  and IGZO  $^{[16]}$  TFTs.

Devices carried out with positive gate bias stress (PGBS), have showed a hump effect [17] and positive  $V_T$  shift [14] due to trap densities and with little or no change in S and  $\mu$ . Nevertheless, it has been exceptions, reporting an increase in mobility [18] attributed to trapping/detrapping and negative  $V_T$  shifts in the case of HfO2 [19].

In a previous work [20], we reported all RF magnetron sputtering at room temperature HIZO TFTs with  $HfO_2$  as gate dielectric and metal-insulator-semiconductor (MIS) structures, with low operation voltage range. Since these devices are suitable to work at low operation voltages, in this work we analyze the stability in NGBS and PGBS, as well as the contact resistance with Al as metal contact. As far as we know, this is the first time this study is presented for devices with  $HfO_2/HIZO$  layers, both deposited by RF sputtering at room temperature.

## II. EXPERIMENTAL PART

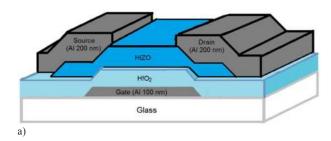

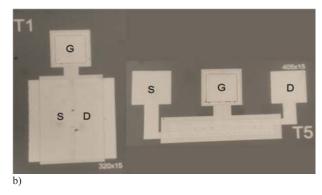

AOSTFTs were fabricated using a corning glass as substrate, cleaned by RCA. Then,  $100 \,\mathrm{nm}$  of Al were deposited by thermal evaporation as bottom gate contact. Then,  $140 \,\mathrm{nm}$  of  $\mathrm{HfO}_2$  and  $40 \,\mathrm{nm}$  of  $\mathrm{HIZO}$  (Hf:In:Zn = 0.3:1:1 mol%) were deposited by RF sputtering at room temperature. HIZO and  $\mathrm{HfO}_2$  films were patterned by standard photolithography and wet and dry etching, respectively. Finally, 200 nm of Al were deposited and patterned by lift-off technique for the S/D top contacts. Cross section and top view of the devices are shown in Fig.1.

Fig. 1 a) Cross-section of HIZO TFTs. b) Top overview of two different fabricated transistors showing the two different layouts with W=320  $\mu$ m (left) and W=405  $\mu$ m (right).

Gate bias stress was performed for 5 minutes at  $V_G^{=\pm}6V$ . The transfer characteristics were measured before and after applying the stress. Hysteresis was also measured and analyzed with hysteresis. The I-V measurements were performed using a Keithley 4200 semiconductor characterization system at room temperature in the dark.

#### III. ANALYSIS AND DISCUSSION

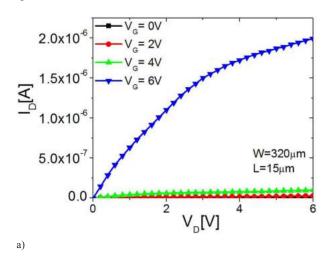

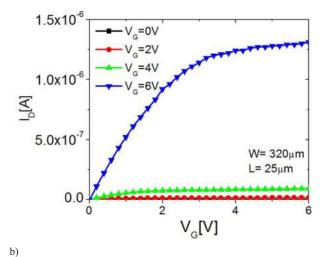

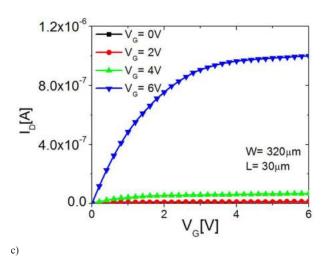

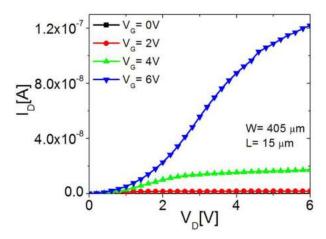

Figure 2 shows the output characteristics of three devices with different channel length (L): 15, 20, 25 and 30 μm. As can be observed, there is significant increase in drain current when the gate voltage changes from 4 to 6 V. A similar behavior was found for IGZO-TFTs, which was attributed to the formation of oxide at the interfacial layer between Mg doped IGZO and Ti electrodes<sup>[21]</sup>.

Fig. 2 Output characteristics of HIZO TFTs with W=320  $\mu$ m and a) L=15  $\mu$ m b) L= 25  $\mu$ m c) L=30  $\mu$ m.

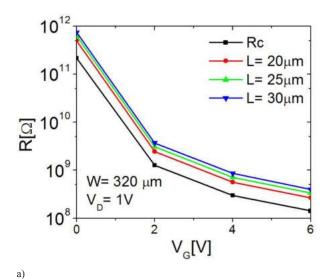

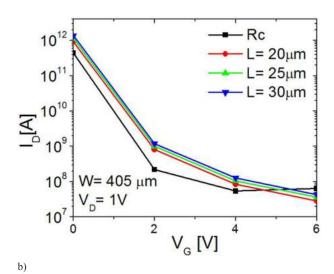

As ZnO-based materials are oxide semiconductors and both, Al and Ti, are highly sensitive to oxygen<sup>[22,23]</sup>, a dielectric interlayer can be formed at the S-D/active layer interface affecting the performance of the devices. Therefore, it is important to be analyze the presence of a contact resistance ( $R_c$ ). This effect was analyzed in our structures using the transmission-line method (TLM)<sup>[24]</sup> for the two different layouts (Fig 1b). As can be seen in Fig. 3 that, devices with W= 405 µm have a higher channel resistance ( $R_{ch}$ ) and  $R_c$  than devices with W= 320 µm, which can be explained due to the lower contact area for the first case. This contact effect is observed also in the output characteristics in Figure 4. Also, it is observed a drain current of  $10^{-7}$  A, an order of magnitude lower than devices with W= 320 µm.

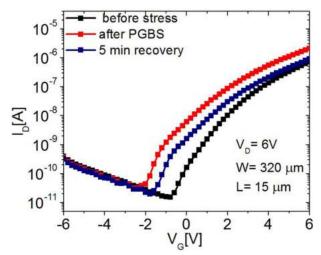

Devices with the lowest R<sub>c</sub> were analyzed in PGBS and NGBS. In Fig. 5, after PGBS it is observed a hump-effect, as well as, V<sub>T</sub> shift to the left in the transfer curves. This V<sub>T</sub> shift has been previously attributed to the increase of the trapped charge density at the dielectric/active layer interface<sup>[10, 25]</sup>. A similar behavior was found also for devices with HfO<sub>2</sub> deposited by ALD<sup>[26]</sup>.

Fig. 3 Rc and Rch of devices with a) W=320 μm and b) 450 μm.

Fig. 4 Output characteristic of HIZO TFTs with W=405  $\mu m.$

It has been found that  $V_T$  shifts in the negative direction after PGBS due to the reversible charge/discharge effect of the electrons in pre-existing high-k  $HfO_2$  bulk traps[26] and do not cause any degeneration as it can be observed in Fig. 5, that stressed devices tend to recover after 5 mins.

Fig. 5 Transfer characteristics of HIZO TFTs with PGBS and recovery after 5 min.

Trap density at the interface after PGBS was found to increase up to  $3.1x10^{11}$  cm<sup>-2</sup> while mobility varies from  $6x10^{-2}$  to  $1.3x10^{-1}$  cm<sup>2</sup>/V·s. Estimated VT shifting ( $\Delta V_T$ ) was 0.5 V.

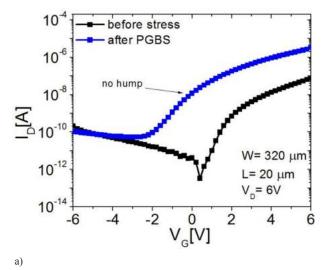

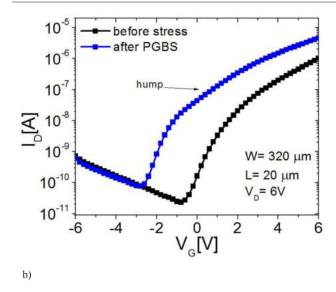

In Fig. 6a and 6b, VG was swept from 6 to -6 V and vice versa, respectively, after PGBS, where both presented a negative VT shift and a "hump" appeared for the latter. This "hump" could be explained by when a negative  $V_G$  is applied, the density of states N at the back of the active layer is sufficiently high and the electron concentration near the back interface remains high enough to provide a current path in parallel to the TFT channel requiring more negative gate voltage to be applied to finally turn off the device, which gives rise to this hump<sup>[27]</sup>.

Fig. 6 Transfer characteristics of HIZO TFTs with PGBS with VG sweep: (a) VG=6 to -6 V and (b) VG=-6 to 6 V.

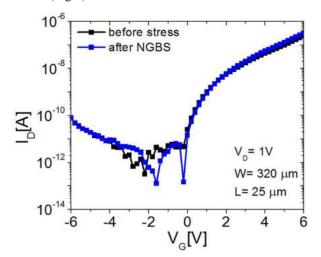

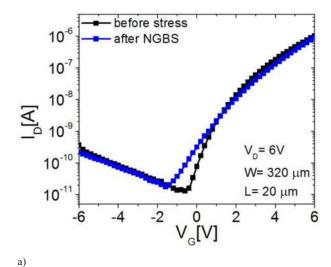

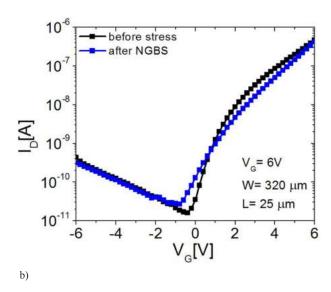

NGBS did not seem to affect the behavior of the devices in the linear regime, neither a  $V_{\rm T}$  shift nor a hump was observed (Fig 7).

Fig. 7 Transfer characteristic of HIZO TFTs with NGBS in the linear regime.

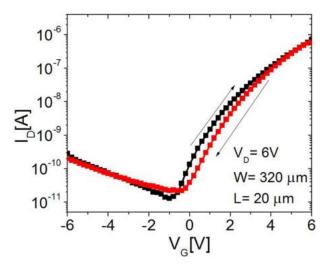

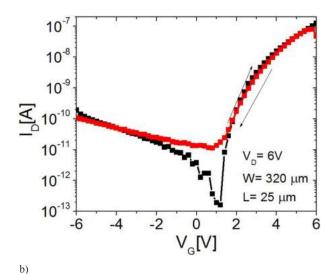

In the transfer curves in saturation (Fig.8), the V<sub>T</sub> shift is not observed, but shape of the transfer curve is slightly modified indicating the presence of interface traps. When NGBS is applied, the transistor channel is depleted of electrons at the channel/dielectric interface and no mobile negative charges are available for the charge trapping and tunneling process<sup>[7]</sup>. Despite oxide fixed charge centers are immobile, the deformation of the curve can be due to mobile ions that alter the centroid of the mobile ion distribution<sup>[28]</sup>.

Fig. 8 Transfer characteristics of HIZO TFTs with NGBS in saturation regime.

Figure 9 shows the hysteresis behavior of two HIZO TFTs with different L.  $V_H$  shift of  $V_G$  in hysteresis loops is commonly attributed to the polarization of the dielectric or to the interface trap density and/or bulk trap density<sup>[29]</sup>. Hysteresis loop here is quite small and since  $HfO_2$  is a high-k dielectric, the shift is expected to be caused by the orientation of the dielectric dipoles when bias is applied.

Flores, Hernández, garduno, Mejía, Estrada

Fig. 8 Hysteresis characteristics of HIZO TFTs.

### IV. Conclusion

The effects of gate-bias stress on the characteristics of HfO<sub>2</sub>/HIZO-TFTs, with both layers deposited by room temperature RF sputtering, were analyzed for the first time.

Devices show bias stress-induced instability as the  $V_{\scriptscriptstyle \rm T}$ shifts toward negative values which be related to properties of the HfO, and/or its interface to the HIZO channel layer or to the reversible charge/discharge effect of the electrons in pre-existing high-k HfO, bulk traps. PGBS do not cause any degeneration, since stressed devices tend to recover after 5 mins. However, further work is required to a better understanding of the specific mechanisms involved. The charge/discharge effect can be reduced with a decrease in pre-existing high-k bulk traps and reducing the interlayer thickness.

Devices under NGBS showed a slight shift since the transistor channel is depleted of electrons at the channel/ dielectric interface and no mobile charges are available for the charge trapping and tunneling process when a negative bias is applied to the gate.

Hysteresis loop was small in spite of using a high-k dielectric. Despite a high parasitic resistance, due to the interlayer formed Al used as S-D contacts interlayer formed, the HIZO devices work at voltage lower than 6 V.

## ACKNOWLEDGEMENTS

This work was supported by CONACYT Project 237213 and partially funded by CONACYT project CB-2014/240103.

#### REFERENCES

- E. Fortunato, P. Barquinha, R. Martins," Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances", Adv. Mater. Vol. 24, pp. 2945-2986, (2012).

- Chang-Jung Kim, Sangwook Kim, Je-Hun Lee, Jin-Seong Park, Sunil Kim, Jaechul Park, Eunha Lee, Jaechul Lee, Youngsoo Park, Joo Han Kim, Sung Tae Shin, and U-In Chung Applied Physics Letters 95, 252103 (2009)

- J.-Y. Kwon, J.S. Jung, K. S. Son, K.-H. Lee, J. S. Park, T. S. Kim, J.-S. Park, R. Choi, J. K. Jeong, B. Koo, S. Y. Lee, "The impact of gate dielectric materials on the light-induced bias instability in Hf-In-Zn-O thin film transistor", Appl. Phys. Lett. 97, 183503, (2010).

- K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono, "All oxide transparent MISFET using high-k dielectrics gates" Microelectr. Eng., vol. 72, pp. 294-298, (2004).

- I. Hernandez, M. Estrada, I. Garduno, J. Tinoco, A. Cerdeira, "Characterization of HfO, on Hafnium-Indium-Zinc Oxide HIZO layer Metal-Insulator-Semiconductor Structures deposited by RF sputtering", Microelectronics Technology and Devices (SBMicro), 30th Symposium, August 2015.

- [6] P. Gorn, M. Lehnhardt, T. Riedl, and W. Kowalsky "The influence of visible light on transparent zinc tin oxide thin film transistors", Appl. Phys. Lett., vol. 91, no. 19, p.193 504, (2007).

- A. Suresh and J.F. Muth "Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors" Appl. Phys. Lett., vol. 92, no. 1, p. 013502, (2009)

- K.T. Kim, k. Lee, M. S. Oh, and S. Im, "Surface induced time dependent instability of Zno-based thin film transistors", Thin Solid Films, vol. 517, no. 23, pp. 6345-6348, (2009).

- J. K. Jeong, H. W. Yang, J. H. Jeong, Y. G. Mo, and H. D. Kim, "Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors," Appl. Phys. Lett., vol. 93, no. 12, p. 123 508, (2008).

- [10] J.H. Shin, J.S. Lee, C.S. Hwang, S. H. K. Park, W. S. Cheong, M. Ryu, C. W. Byun, J. I. Lee, and H. Y. Chu, "Light effects on the bias stability of transparent ZnO thin film transistors" ETRI J., vol. 31, no. 1, pp. 62-64, (2009).

- [11] D.C. Paine, B. Yaglioglu, Z. Beiley, and S. Lee, "Amorphous IZObased transparent thin film transistors", Thin Solid Films, vol. 516, no.17, pp. 5894-5898, (2008).

- [12] Lopes, M. E., Gomes, H. L., Medeiros, M. C. R., Barquinha, P., Pereira, L., Fortunato, E., R. Martins, and I. Ferreira, "Gate-bias stress in amorphous oxide semiconductors thin-film transistors." Appl. Phys. Lett., 95(6), 063502, (2009).

- [13] J. F. Conley, Instabilities in amorphous oxide semiconductor thin-film transistors. IEEE Transactions on Device and Materials Reliability, vol. 10, no 4, p. 460-475, (2010).

- [14] J.M. Lee, I.T. Cho, J.H. Lee, and H. I. Kwon, "Bias stress induced stretched exponential time dependence of threshold voltage shift in InGaZnO thin film transistors." Appl. Phys. Lett., vol. 93, no. 9, p. 093504, (2008).

- [15] P. T. Liu, Y.T. Chou, and L. F. Teng, "Environment-dependent metastability of passivation-free induim zinc oxide thin film transistor after gate bias stress" Appl. Phys. Lett. vol. 95, no. 23, p.233 504, (2009).

- [16] H.H. Lu, H. C. Ting, T. H. Shih, C.Y. Chen, C. S. Chuang, and Y. Lin "76.3:32-inch LCD panel using amorphous indium-gallium-zinc oxide TFTs" in Proc. SID Dig., pp. 1136-1138, 2010.

- [17] Mativenga, M., Seok, M., & Jang, J. "Gate bias-stress induced humpeffect in transfer characteristics of amorphous-indium-galium-zincoxide thin-fim transistors with various channel widths", Appl. Phys. Lett., 99(12), 122107, (2011).

- [18] A. J. Flewitt, J. D. Dutson, P. Beecher, D. Paul, S. J. Wakeham, M. E. Vickers, C. Ducati, S.P. Speakman W.I. Milne, M. J. Thwaites, "Stability of thin film transistors incorporating a zinc oxide or indium zinc oxide channel deposited by a high rate sputtering process", Semicon. Sci. and Tech., 24(8), 085002, (2009).

- [19] Hoffman, R., Emery, T., Yeh, B., Koch, T., & Jackson, W. "21.4: Zinc Indium Oxide Thin-Film Transistors for Active-Matrix Display Backplane", SID Symposium Digest of Technical Papers Vol. 40, No. 1, pp. 288-291. Blackwell Publishing Ltd, (2009, June).

- [20] C.A. Pons-Flores, I. Hernandez, M. Estrada, I. Garduño, A. Cerdeira, I. Mej {ia, J. Tinoco, R. Picos, "Hafnium-Indium-Zinc Oxide thin film transistors using HfO<sub>2</sub> as gate dielectric, with both layers deposited by RF sputtering", Microelectronics Technology and Devices (SBMicro), 31st Symposium, August 2016

- [21] Wu, Hung-Chi, Tung-Sheng Liu, and Chao-Hsin Chien. "Effect of Mg Doping on the Electrical Characteristics of High Performance IGZO Thin Film Transistors." ECS Journal of Solid State Science and Technology 3.2, Q24-Q27, (2014).

- [22] Crowell, J. E., J. G. Chen, and J. T. Yates. "Surface sensitive spectroscopic study of the interaction of oxygen with Al (111)-low temperature chemisorption and oxidation." Surface science 165.1, 37-64, (1986).

- [23] Nyberg, C. "The reaction of oxygen with Ti, Cr, Fe and Ni studied by appearance potential spectroscopy." Surface Science 52.1, 1-9, (1975).

- [24] Cerdeira, A., Estrada, M., Marsal, L. F., Pallares, J., & Iñiguez, B. "On the series resistance in staggered amorphous thin film transistors", Microelectron. Rel., 63, 325-335, (2016).

- [25] Cerdeira, A., Estrada, M., Soto-Cruz, B.S. and Iñiguez, B, "Modeling the behavior of amorphous oxide thin film transistors before and after bias stress", Microelectron. Rel. 52, 2532-2536, (2012).

- [26] S.H. Ho, T.C. Chang, Y.H. Lu, C.E. Chen, J.Y. Tsai, K.J. Liu, T.Y. Tseng, O. Cheng, C.T. Huang, C.S. Lu, "Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO2 structure using fast I-V measurement", Appl. Phys. Lett. 104, 113503, (2014).

- [27] Estrada, Cerdeira, Iñiguez, "Effect of interface charge on the dc bias stress-induced deformation and shift of the transfer characteristic of amorphous oxide thin-film transistors", Microelectron. Rel. 52,pp. 1342-1345, (2012).

- [28] E. H. Nicollian, J. R. Brews. MOS (Metal Oxide Semiconductor), Physics and Technology. New York, NY, USA: Wiley, 2003.

- [29] Yun, M. G., Kim, S. H., Ahn, C. H., Cho, S. W., & Cho, H. K., "Effects of channel thickness on electrical properties and stability of zinc tin oxide thin-film transistors", J. of Phys. D: Appl. Phys., 46(47), 475106, (2013).